锁相环pll工作原理及verilog代码(pll锁相环 fpga)

admin 发布:2024-01-08 21:40 68

本篇文章给大家谈谈锁相环pll工作原理及verilog代码,以及pll锁相环 fpga对应的知识点,希望对各位有所帮助,不要忘了收藏本站喔。

本文目录一览:

pll的locked信号

1、PLL - PHASE-LOCKED LOOP 中文称锁相环, 它的基本作用是把频率锁定在一个固定的期望值,它由压控振荡器VCO、鉴相器PD、分频器、电荷泵和低通滤波器组成。

2、Locked信号是用来观察pll输出时钟是否和输入时钟锁定。当锁定时,这个Locked信号就变为高电平。

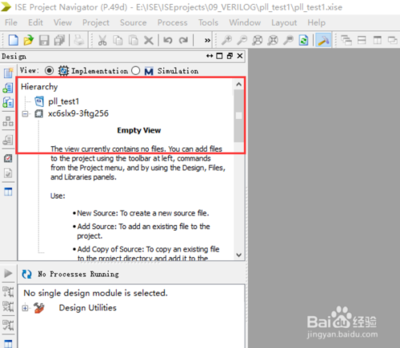

3、RESET即整个PLL的复位信号,LOCKED则是PLL输出时钟正常工作的指示信号。完成上面的配置,在Page5中,如图所示,所有相关的配置信息都在此罗列出来了,供review。

4、如果你的PLL是全局时钟的话,这个方法没有问题,这也是一种常用方法。另外,对寄存器初始化,利用异步复位即可。

5、PLL后scale计数器G0或G1 全局时钟网络(1)e0(2)PLL时钟输出驱动单端或LVDS外部时钟输出管脚。PLL后scale计数器E PLL[.1]_OUT管脚(3)locked PLL锁定状态。当PLL锁定时,该端口为高。当PLL失锁时,该端口为低。

锁相环原理

1、锁相环是一种用于恒定频率的电路。它通常由一个振荡电路和一个锁相控制电路组成。振荡电路的作用是产生频率接近但不精确的正弦信号。

2、所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位 误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简 称环路,通常用PLL表示。

3、正弦波相位检波器这种鉴相器实际上是一个平衡混频器,它的原理图如下: 但是它是一种要求平衡度比较高的检波电路,平衡对称性很重要。

4、模拟锁相环核心是压控振荡器,检测输出频率,转换为电压,控制压控振荡器的频率,当输入和输出同相时控制达到稳定.数字锁相环主要检测输入和输出时钟的相位关系,通过正反馈和负反馈的分频,可以将输入时钟分频、倍频或跟踪等。

基于Verilog的数字锁相环设计源代码

1、设置开锁密码,并按此密码设计电路。密码可以是0~9十位数。若按开锁编码规定数的先后顺序按动按钮后,发光二极管由灭变亮,表示电子锁打开。通过扫描按键,并与原设置的密码校验,正确则控制二极管。

2、下面是一个简单的 Verilog HDL 代码,可以实现六位数码管动态显示从左到右为123456的效果。

3、每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

4、其实很简单的,这个和可以设置初始值的计数器实现方法是一样的。如果你能看懂下面这段代码,相信你肯定能写出一个模值可变的计数器了。

5、在Verilog中,可以声明两种不同的过程:always过程和initial过程。过程可以是包含时序的过程描述,而不包含时序的过程还可以表达组合逻辑。

电路锁相环的是怎么工作的?

1、所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位 误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简 称环路,通常用PLL表示。

2、锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的。

3、模拟锁相环主要由相位参考提取电路、压控振荡器、相位比较器、控制电路等组成。

4、锁相环是一种用于恒定频率的电路。它通常由一个振荡电路和一个锁相控制电路组成。振荡电路的作用是产生频率接近但不精确的正弦信号。

锁相环测量频率的原理?

1、它的工作原理是通过对输入信号进行倍频,使输出信号的频率是输入信号的整数倍。锁相环倍频器的关键部分是振荡电路,其中包含一个振荡器和一个相位比较器。

2、锁相环是一种用于恒定频率的电路。它通常由一个振荡电路和一个锁相控制电路组成。振荡电路的作用是产生频率接近但不精确的正弦信号。

3、所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位 误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简 称环路,通常用PLL表示。

4、锁相环是以接收到的信号的频率和相位,通过负反馈的方式,使得机内其它电路的本振信号能够与它同步,频率同步、相位同步,以便在后面的鉴相鉴频等正确工作。锁相环与变频器不同。

PLL(锁相环)工作原理是﹖

1、其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2、PLL - PHASE-LOCKED LOOP 中文称锁相环, 它的基本作用是把频率锁定在一个固定的期望值,它由压控振荡器VCO、鉴相器PD、分频器、电荷泵和低通滤波器组成。

3、锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

4、由于控制电压vr的变化,VCO振荡频率会提高。结果使得fr=f。在f与f的相位成为一致时,PD端子会成为高阻抗状态,使PLL(锁相环)被锁栓(Lock)。

关于锁相环pll工作原理及verilog代码和pll锁相环 fpga的介绍到此就结束了,不知道你从中找到你需要的信息了吗 ?如果你还想了解更多这方面的信息,记得收藏关注本站。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

- 上一篇:公司网站开发后台代码的简单介绍

- 下一篇:ie兼容代码(xbox无法连接无线网络)

相关推荐

- 05-02ajax删除代码(ajax 增删改查)[20240502更新]

- 05-02js代码3d图片叠加旋转切换(js图片绕中心旋转的代码)[20240502更新]

- 05-02代码如何实现导航栏(做导航栏代码)[20240502更新]

- 05-02做网页菜单栏设计代码(网页设计菜单栏导航实例)[20240502更新]

- 05-02js颜色代码(js颜色代码对照表)[20240502更新]

- 05-02百度空间c代码(百度空间c代码是多少)[20240502更新]

- 05-02淘宝右侧导航条css代码(淘宝右侧导航条css代码)[20240502更新]

- 05-02cs游戏代码(cs进入游戏代码)[20240502更新]

- 05-02vb代码注册控件(vb 注册表)[20240502更新]

- 05-02popup弹出层代码(popupwindow底部弹出)[20240502更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接