veriloghdl代码(verilog hdl语言100例详解)

admin 发布:2023-10-06 07:15 92

本篇文章给大家谈谈veriloghdl代码,以及verilog hdl语言100例详解对应的知识点,希望对各位有所帮助,不要忘了收藏本站喔。

本文目录一览:

用verilog设计一个4位4输入最大数值检测电路。拜托大神帮下忙_百度知...

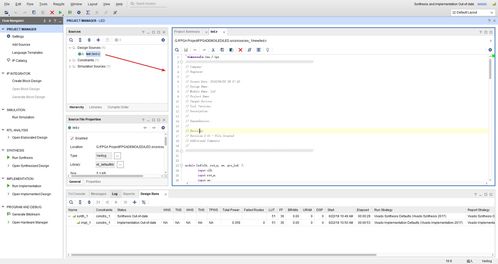

1、设计任务及原理:LED循环显示控制电路就是对于一组LED(16个),通过不同的工作模式可按照一定的规律来点亮或者熄灭。

2、选1数据选择器使用两位地址码A1A2产生4个地址信号,由A1A2等于“00”、“01”“10”“11”来选择输出。输入信号:4个数据源d0、ddd3。两位地址码a[.0];使能端g。输出信号:输出选择则端y。

3、实现N位Johnson Counter,N=5。(南山之桥) 5用你熟悉的设计方式设计一个可预置初值的7进制循环计数器,15进制的呢?(仕兰 微电子) 60、数字电路设计当然必问Verilog/VHDL,如设计计数器。

4、前级是一个比较器,使用在开集状态,在此电路里充当二极管与后面的电容一起组成峰值检波电路,但由于比较器的滞后会产生较短的时间差。

5、因为4位数码管的段控制输入是复用的,要分别显示不同的计数数值,需要 使用动态扫描显示技术,其电路结构如图61 所示。

verilog里面“**”代表什么?

1、verilog里面** 表示这是多少次幂。

2、Verilog是一种硬件描述语言,而always @(*)是Verilog中常用的一种代码结构。它表示在任何输入信号变化时,这一段代码都会触发执行。

3、在Verilog HDL语言有一个特殊的运算符:位拼接运算符{},用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。

4、在Verilog中always@(*)语句的意思是always模块中的任何一个输入信号或电平发生变化时,该语句下方的模块将被执行。always语句有两种触发方式。

5、是的,这里的*号代替了本always模块里面所有的触发信号。

veriloghdl代码的介绍就聊到这里吧,感谢你花时间阅读本站内容,更多关于verilog hdl语言100例详解、veriloghdl代码的信息别忘了在本站进行查找喔。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

- 上一篇:论坛美化代码大全(discuz)

- 下一篇:VB股票实时价格代码(股票vb是什么)

相关推荐

- 05-02管理代码(企业管理代码)[20240502更新]

- 05-02包含跟屏悬浮客服代码的词条[20240502更新]

- 05-02修饰网页代码(网页设计修改)[20240502更新]

- 05-02音乐播放器网页代码(HTML音乐播放器代码)[20240502更新]

- 05-02谷歌离线地图apicss代码(谷歌地图接入)[20240502更新]

- 05-02html5导航条代码生成器(html导航条制作)[20240502更新]

- 05-02functionmatlab代码(matlab出现function)[20240502更新]

- 05-02js变圆代码(图片变圆的代码)[20240502更新]

- 05-02关于类似于漂流瓶html代码的信息[20240502更新]

- 05-01jqtab代码的简单介绍[20240501更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接