fpga电子琴源代码verilog(fpga课程设计电子琴)

admin 发布:2022-12-19 08:46 99

今天给各位分享fpga电子琴源代码verilog的知识,其中也会对fpga课程设计电子琴进行解释,如果能碰巧解决你现在面临的问题,别忘了关注本站,现在开始吧!

本文目录一览:

- 1、FPGA verilog 代码解读!!!求助!!!

- 2、关于verilog代码在FPGA上实现的问题

- 3、FPGA中,用Verilog实现的程序,求大神帮忙分析一下程序

- 4、怎样用verilog写FPGA的代码

FPGA verilog 代码解读!!!求助!!!

初步来看,这段代码是在检测到PinIn的下降(1-0)时,启动counter计数,计到50000次后,在PinIn无输入的情况下,PinOut assign为rPinOut输出一个周期的1。

但这段代码明显是学生写的,不会是工程师,有些地方的写法不严谨:

1、最首要的,这个模块没有复位,这在哪种设计里都是不允许的。

2、if没有跟else来收束条件分支,就是说存在没有覆盖到的情况,不够严谨。

3、同一个always块里做了太多的事情,一般推荐是一个always块只干一件事,好处是代码可读性好,而且逻辑简洁,不容易出错

关于verilog代码在FPGA上实现的问题

哈哈,自己写好代码就可以了,由软件自动造成网表。

布局,布线也是由软件自动规划在FPGA芯片里面的连接问题。(注意是芯片里面的连接)规划好了,下载进芯片的话,芯片里面就是那种规划的结构了

(理解成没有下载程序的芯片是一张白纸)。

至于管脚分配就举个例子吧,假如你写了一个2选一的选择器。

输入端口有a,b,sel.输出口有c

你得把a,b,sel,c分配到FPGA芯片上的具体某个管脚。

下载完后,芯片上那几个脚就相当于这个选择器的脚了。

FPGA中,用Verilog实现的程序,求大神帮忙分析一下程序

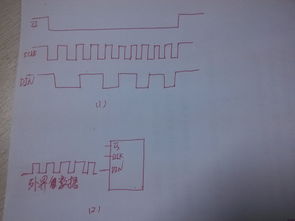

module d_asyn(clk,clr,d,q); //模块输入输出口,共四个信号,每个都是1bit的

input clk,clr,d; //这些是作为输入

output q; //这些是作为输出

reg q; //q在作为寄存器类的输出,就是说可以用= 箭头赋值(见下面)

always @(posedge clr) //posedge:上升沿。就是说在clr信号的上升沿的时候都会触发这个操作

begin //可以忽略,就是多条语句在一块的时候要用

q=0; //清0

end

always @(necedge clk) //negedge:下降沿,你肯定拼错了 ,在clk下降沿的时候触发

begin

#10 q=d; //延迟10个单位,这个在#timescale那里定义,这个只在仿真的时候有用,在器件上的时候不能这样做延迟

end

endmodule

怎样用verilog写FPGA的代码

对于FPGA设计,先要熟悉FPGA的内部结构,然后才知道怎么去调用内部资源。它与ASIC或SOC设计有很大的不同。

关于fpga电子琴源代码verilog和fpga课程设计电子琴的介绍到此就结束了,不知道你从中找到你需要的信息了吗 ?如果你还想了解更多这方面的信息,记得收藏关注本站。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

相关推荐

- 05-16线下课程seo,线下课程的好处和弊端

- 05-15智推教育seo课程,智推app

- 05-14长沙设计优化公司,长沙设计优化公司招聘信息

- 05-14网站怎么设计,网站怎么设计怎么实现的

- 05-08网站设计的好处,设计网站的目的

- 05-07pb超级报表源代码(pb报表工具)[20240507更新]

- 05-07简历源代码可以上传照片的简单介绍[20240507更新]

- 05-07广告切换源代码免费下载(广告切换源代码免费下载安装)[20240507更新]

- 05-06阁楼网源代码(阁楼是什么网站)[20240506更新]

- 05-06源代码管理资源管理器(资源管理器运行代码)[20240506更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接