verilog实例代码(verilog编程实例)

admin 发布:2023-09-11 00:30 102

本篇文章给大家谈谈verilog实例代码,以及verilog编程实例对应的知识点,希望对各位有所帮助,不要忘了收藏本站喔。

本文目录一览:

- 1、verilog怎么函数调用

- 2、谁能帮忙翻译一下这个verilog程序

- 3、32MHZ的时钟,在FPGA中用Verilog语言编写一个5us的死区程序,请教各位...

- 4、在verilog模块中,常见的并行语句块有哪些?其中哪些是可综合的verilog语句...

- 5、在verilog中,模块实例化能用在always吗?

- 6、在verilog中如何将一段代码加到另一段代码中

verilog怎么函数调用

要想在FPGA硬件里面实现随机数,首先用rom的方法产生01随机数,然后在看你想要产生哪种分布的随机数,在用反函数的方法实现。

task定义可以没有输入。function必须至少输入 function智能与主模块共用同一个仿真时间单位,而task可以定义自己的方阵时间单位 function要有返回值,返回一个值,而task不需要返回值。

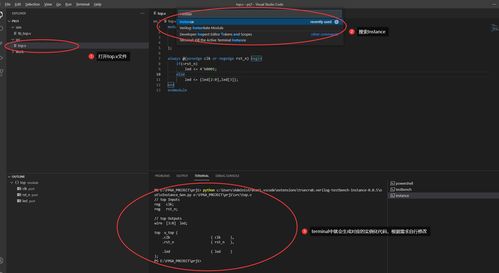

verilog在调用模块的时候,信号端口可以通过位置或名称关联。

module topmod();...submod1 u1(...); //这里就是调用子模块 submod2 u2(...);endmodule module submod1(...)...endmodule module submod2(...)...endmodule 上述所有放主程序topmod.v里即可。

调用底层模块就是在顶层模块中实例化底层模块,参数的话,在实例化的时候进行重新定义。

谁能帮忙翻译一下这个verilog程序

这些都是自己定义的端口名称,不是固有函数。

wire clk,reset;的确是多余的。按照标准如果没有显示说明,都认为是wire类型。idle在这里是表示所有其它未定义状态均回归idle状态。是电路未知状态稳定性回归描述的一部分。

这是一个任务。这个任务是用来设置置位信号拉高和拉低持续的时钟周期数。(posedge clk);是一个触发事件,即当clk上升沿时触发,其实该事件什么也没做,在这里只是起了一个时钟周期延迟的功能。

下面这段always是控制cnt和cnt1计数,大概意思是如果cnt大于8时:首先将cnt清零,接着如果cnt1等于9,将cnt1清零,否则cnt1加1;如果cnt不大于8时,则cnt每次加2。

32MHZ的时钟,在FPGA中用Verilog语言编写一个5us的死区程序,请教各位...

1、reg q; //q在作为寄存器类的输出,就是说可以用= 箭头赋值(见下面)always @(posedge clr) //posedge:上升沿。

2、这是一个 RAM的程序。这里面用到了类似 数组 的概念。reg[7:0] Memory [63:0]; 这个定义表示 64 个 8bits 数。

3、首先PLL应用就不用说明了,这个直接调用内部软核来实现,没有涉及到代码。就分频代码我简单写个8分频的代码,其他的大同小异。

4、fpga和你之前学过的单片机之类的不一样的 labview里是有设定程序的运行时间这个说法 但是fpga没有,fpga的运行时间是根据你用的开发板的,现在比较常见的就是50MHZ的时钟,就是20ns一个clk。

5、用Verilog语言实现任意整数分频器 分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛(Xil)的DLL.来进行时钟的分频,倍频以及相移。

在verilog模块中,常见的并行语句块有哪些?其中哪些是可综合的verilog语句...

可综合的都是并行执行的。其实也不难理解,verilog是硬件语言,也就可以看成是一个电路。在实际的电路中没办法延迟,没办法让一边先通电,再让另一边通电,所以一切都是同时进行的。这并行的前提都是“可综合”。

always块 (1)既可描述组合逻辑,也可也可描述时序逻辑;(2)内部语句顺序执行,块间语句并行执行。

always 不是循环语句,always 是一个进程块。 always@(A or B or C)我们经常能看到的always语句如上面那句,当括号里的A,B或C信号发生变化的时候,这个ALWAYS模块就被激活,模块中的语句才能执行。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。Verilog模型可以是实际电路的不同级别的抽象。

综合就是把你写的rtl代码转换成对应的实际电路。

begin end块中,非阻塞赋值=是并行执行的,所有的值都是同时更新,多用于时序逻辑 阻塞赋值=是顺序执行的,常见于组合逻辑。

在verilog中,模块实例化能用在always吗?

模块实例化不能在always block里面做。

always里面好像不能调用模块的,只能调用任务和函数。

always语句里面是不能调用另一个模块的,其实这个问题的产生是因为你没有理解硬件中各个部分是并行执行的这个特点,你的思维方式属于软件的思维方式。

学习Verilog语法 模块定义、接口定义、模块例化、寄存器定义、线定义、always块 Verilog与软件语言最大的区别:他是描述电路的,写法固定。

在verilog中如何将一段代码加到另一段代码中

在Verilog HDL语言有一个特殊的运算符:位拼接运算符{},用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。

output reg [7:0] cn_out, cd_out; //加结果 output c_neg; //结果的符号。

代码都会写还不会例化模块么?在写一个顶层模块,然后例化第一个模块,给上信号,然后把输出信号连到第二个模块上就可以。

在Verilog中,可以通过定义一个模块并在模块中使用buf语句实现插入buffer的操作。例如以下代码:module buffer_module(input a, output z);buf b(a,z);endmodule 该模块定义了一个输入端点a和一个输出端点z。

低四位是din,高四位是fifo[3:0]。

选择User Document创建自定义的文本文件,文件名和后缀随意。创建好后,在下方切换到Files面板,双击打开该文件,按照自己喜欢的形式输入数据。

关于verilog实例代码和verilog编程实例的介绍到此就结束了,不知道你从中找到你需要的信息了吗 ?如果你还想了解更多这方面的信息,记得收藏关注本站。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

相关推荐

- 05-02管理代码(企业管理代码)[20240502更新]

- 05-02包含跟屏悬浮客服代码的词条[20240502更新]

- 05-02修饰网页代码(网页设计修改)[20240502更新]

- 05-02音乐播放器网页代码(HTML音乐播放器代码)[20240502更新]

- 05-02谷歌离线地图apicss代码(谷歌地图接入)[20240502更新]

- 05-02html5导航条代码生成器(html导航条制作)[20240502更新]

- 05-02functionmatlab代码(matlab出现function)[20240502更新]

- 05-02js变圆代码(图片变圆的代码)[20240502更新]

- 05-02关于类似于漂流瓶html代码的信息[20240502更新]

- 05-01jqtab代码的简单介绍[20240501更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接