m序列verilog代码(m序列特性)

admin 发布:2022-12-19 23:33 177

本篇文章给大家谈谈m序列verilog代码,以及m序列特性对应的知识点,希望对各位有所帮助,不要忘了收藏本站喔。

本文目录一览:

- 1、m序列Verilog程序,多项式为1+X^2+X^3,在线等。。。

- 2、用verilog语言写的的BPSK数字调制器代码

- 3、用verilog DHL语言设计一个5阶的M序列信号发生器,生成多项式位:f(x)=X^5+X^2+1

- 4、急救 用verilog HDL语言设计一个m序列的生成程序

- 5、急救 用verilog HDL语言设计一个m序列的生成程序,您之前有有解决过相关问题。

- 6、谁帮我用verilog语言做个M=15的m序列码发生器

m序列Verilog程序,多项式为1+X^2+X^3,在线等。。。

我这几天正好碰上这个问题,看楼主貌似问问题的时间挺早了,不过还是分享一下经验,给更多和我一样的新手们提供一点帮助。

module m_sequences(clk,signal);

input clk;

output signal;

reg signal;

reg c1,c2,c3;

reg c0=1;

always@(posedge clk)

begin

c3=c2;

c2=c1;

c1=c0;

c0=c3 + c2 ;

signal=c3;

end

endmodule

具体细节可以看一些关于通原方面的知识,其实就是几个反馈移位寄存器,很简单

用verilog语言写的的BPSK数字调制器代码

module psk(clk,clr,fcw,angle,M,EN,psk_output);

input[31:0]fcw;//载波频率

input[9:0]angle;//载波相位

input clk,clr;

input M,EN;//M为输入的序列

output [7:0]psk_output;//输出波形

reg [7:0]psk_output;

wire [7:0]psk_zaibo;

mydds dds_ask(

.gclock(clk),

.clr(clr),

.fcw(fcw),

.pcw(angle),

.outputwave(psk_zaibo));//正弦发生模块,产生载波

always@(posedge clk)

begin

if(EN!=0)

begin

if(M==0)psk_output=~psk_zaibo;//M=0时相位为180

else psk_output=psk_zaibo;//M=1时相位为0

end

else psk_output=0;

end

endmodule

②DPSK模块:方式一

module dpsk(clk,clr,fcw,angle,EN,dpsk_output,a,M);

input[31:0]fcw;//载波频率控制字

input[9:0]angle;//载波相位控制字

input clk,clr;//系统时钟,清零信号

input EN;//系统使能信号

output [7:0]dpsk_output;//输出波形

output a,M;//输出产生的M序列与输出波形相对照

reg [7:0]dpsk_output;

wire [7:0]dpsk_zaibo;

reg a;

initial //初始化模块

begin

a=0;//a存放M序列上一码元的值

end

m1 m1(

.gclock(clk),

.EN(EN),

.M_code(M),

.clk(clk_M));//产生M序列

mydds dds_ask(

.gclock(clk),

.clr(clr),

.fcw(fcw),

.pcw(angle),

.outputwave(dpsk_zaibo)); //正弦发生模块,产生载波

always@(posedge clk)

begin

if(EN!=0)

begin

if(M==a)dpsk_output=~dpsk_zaibo;//当前后码元相同时输出波形相位为180

else

begin

dpsk_output=dpsk_zaibo; //当前后码元不同时输出波形相位为0

end

end

else dpsk_output=0;//当系统没使能时,输出为0

end

always@(posedge clk_M)//根据M序列的同步时钟,来存储M序列当前的值,以便与M序列下一值相比较

begin

a=M;

end

endmodule

③DPSK1模块:方式二

module DPSK1(clk,clr,angle,DPSK_zaibo,EN,DPSK_out,M);

input clk,EN,clr;

input[31:0]DPSK_zaibo;//载波频率控制字

input[9:0]angle;//载波相位控制字

output[7:0] DPSK_out;

output M;

reg[7:0]DPSK_out;

reg[9:0]address1,address2;

reg[9:0]address3,address4;

wire[9:0]address;

reg [9:0]dpsk_zaibo1;

wire[7:0]DPSK_out1;

wire[31:0]data_in;

reg a;

initial //初始化地址

begin

address1=0;

address2=0;

address2[9]=1;

a=0;

end

m1 m1(

.gclock(clk),

.EN(EN),

.M_code(M),

.clk(clk_M));//产生M序列

add_fcw add_fcw(

.clr(clr),

.clk(clk),

.fcw(DPSK_zaibo),

.sum(data_in)

);//频率控制字累加

add_pcw add_pcw(

.clr(clr),

.clk(clk),

.pcw(angle),

.data_in(data_in),

.address(address)

); //与相位控制字相加

always@(posedge clk ) //根据前后码元的异同来修正查询地址

begin

if(EN!=0)

begin

address3=address1+address;

address4=address2+address;

if(M==a)dpsk_zaibo1=address3;//前后码元相同时,相位为0

else

begin

dpsk_zaibo1=address4; ;//前后码元不同时,相位为180

end

end

else dpsk_zaibo1=0;

end

sinrom sinrom (

.a(dpsk_zaibo1), // Bus [9 : 0]

.clk(clk),

.qspo(DPSK_out1)); // Bus [7 : 0]//查询正弦查询表

always@(posedge clk_M) /根据M序列的同步时钟,来存储M序列当前的值,以便与M序列下一值相比较

begin

a=M;

end

always@(posedge clk)

begin

DPSK_out=DPSK_out1;

end

endmodule

m序列自己可以再网上查~

用verilog DHL语言设计一个5阶的M序列信号发生器,生成多项式位:f(x)=X^5+X^2+1

assign outdata = M_buf[0];

always@(posedge clk)

begin

if(!rst)

begin

M_buf = 5'b01011;

end

else

begin //5级M序列编码

M_buf[4] = M_buf[0]^M_buf[3];

M_buf[0] = M_buf[1];

M_buf[1] = M_buf[2];

M_buf[2] = M_buf[3];

M_buf[3] = M_buf[4];

end

end

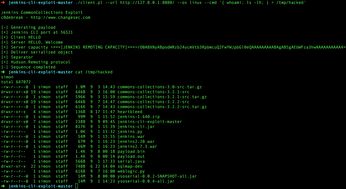

急救 用verilog HDL语言设计一个m序列的生成程序

我m序列代码赋值下来是,发现wire和x中间没有空格,这可能是导致你没有输出的原因,个人建议你的代码这样写:

module

prbs(clk,rst,m_out);

input

clk,rst;

output

m_out;

reg[7:0]

reg_buf;

reg

x;

always@(posedge

clk

or

posedge

rst)

if(!rst)

begin

reg_buf[7:0]

=

8'b1000_0000;

x

=

1'b1;

end

else

begin

reg_buf[7:0]

=

{reg_buf[6:0],x};

x

=

reg_buf[7]^reg_buf[3]^reg_buf[2]^reg_buf[1];

end

assign

m_out

=

reg_buf[7];

endmodule

急救 用verilog HDL语言设计一个m序列的生成程序,您之前有有解决过相关问题。

我m序列代码赋值下来是,发现wire和x中间没有空格,这可能是导致你没有输出的原因,个人建议你的代码这样写:

module prbs(clk,rst,m_out);

input clk,rst;

output m_out;

reg[7:0] reg_buf;

reg x;

always@(posedge clk or posedge rst)

if(!rst)

begin

reg_buf[7:0] = 8'b1000_0000;

x = 1'b1;

end

else

begin

reg_buf[7:0] = {reg_buf[6:0],x};

x = reg_buf[7]^reg_buf[3]^reg_buf[2]^reg_buf[1];

end

assign m_out = reg_buf[7];

endmodule

谁帮我用verilog语言做个M=15的m序列码发生器

module M15Serial(

input c_clk,

input iN_rst,

output o_ser

);

reg [3:0]flow = 4'b0001;

assign o_ser = flow[0];

always@(posedge c_clk or negedge iN_rst)

begin

if(~iN_rst)

flow = 4'b0001;

else

begin

flow[3:1] = flow[2:0];

flow[0] = flow[3] ^ flow[2];

end

end

endmodule

//output o_ser 是序列输出

关于m序列verilog代码和m序列特性的介绍到此就结束了,不知道你从中找到你需要的信息了吗 ?如果你还想了解更多这方面的信息,记得收藏关注本站。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

- 上一篇:点击代码(autojs找图点击代码)

- 下一篇:分页代码php(分页代码实现原理)

相关推荐

- 05-02cs游戏代码(cs进入游戏代码)[20240502更新]

- 05-02vb代码注册控件(vb 注册表)[20240502更新]

- 05-02popup弹出层代码(popupwindow底部弹出)[20240502更新]

- 05-02css3代码大全(html5代码大全)[20240502更新]

- 05-02图片走马灯效果代码(html图片走马灯效果)[20240502更新]

- 05-02html代码蝴蝶(动态蝴蝶的代码)[20240502更新]

- 05-02轮番图代码(图片轮播图代码)[20240502更新]

- 05-02关于人事管理系统代码的信息[20240502更新]

- 05-02网页字体滚动代码(网页设计字体滚动)[20240502更新]

- 05-02拍拍客服悬浮代码(拍拍客服悬浮代码怎么设置)[20240502更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接