放大器verilog源代码(比较器verilog代码)

admin 发布:2022-12-19 21:31 151

今天给各位分享放大器verilog源代码的知识,其中也会对比较器verilog代码进行解释,如果能碰巧解决你现在面临的问题,别忘了关注本站,现在开始吧!

本文目录一览:

- 1、quartus II 中如何用verilog源文件生成原理图

- 2、急!!!led显示屏的Verilog HDL代码

- 3、verilog语言编写源代码和测试程序

- 4、请问在Verilog中模块源代码和测试模块源代码关系

- 5、用verilog设计一个4*4矩阵键盘,来对模拟开关进行控制从而实现对输入电压不同倍数的放大

- 6、我做verilog HDL的练习题,简单时序逻辑电路的设计,在quartus中做的代码在modelsim仿真时出现了错误!

quartus II 中如何用verilog源文件生成原理图

1、打开quartus II,用verilog源文件,先点击file文件,下来菜单点击create/update。

2、然后我们选择右侧的create symbol file for current file生成原理图。

3、打开后界面随意右键弹出下来列表,选择insert。

4、右边出现选择菜单,点击选择symbol。

5、在选择的框中选择点击一个你需要的路径点击即可生成原理图到文件夹。

急!!!led显示屏的Verilog HDL代码

/*****************数码管的静态显示从0到9************************/

//加计数器计数值在一个数码管上显示,k2(en)为低电平时停止加数,

//k1(rst)为低电平时清0 显示的数在0-9之间

//2010-5-23 16:14:07

module shu_jingjia_10(clk,wei,shu,rst,en,led);

input clk,rst,en;

output wei;

output[7:0] shu,led;

reg[7:0] shu_out,led_Out;

reg[25:0] led_out;

reg[3:0] display0;

reg wei_out;

initial led_out=0;

always @(posedge clk)

begin

led_out=led_out+1;

if (led_out==12500000)

begin

led_out=0;

if (en==1)

begin

display0=display0+1;

if (rst==0)

display0=0;

if (display0==10) //加到10 清0

begin

display0=0;

led_out=0;

end

end

end

end

always @(clk)

begin

wei_out=0;

case (display0)

0 : shu_out=8'b1100_0000;

1 : shu_out=8'b1111_1001;

2 : shu_out=8'b1010_0100;

3 : shu_out=8'b1011_0000;

4 : shu_out=8'b1001_1001;

5 : shu_out=8'b1001_0010;

6 : shu_out=8'b1000_0010;

7 : shu_out=8'b1111_1000;

8 : shu_out=8'b1000_0000;

9 : shu_out=8'b1001_0000;

default:shu_out=8'b1111_1111;

endcase

end

assign shu=shu_out;

assign wei=wei_out;

assign led=led_out;

endmodule

verilog语言编写源代码和测试程序

module number_locker( //input

clk,

reset,

data, //input 10 bits data

//output

open

);

input clk,reset;

input[3:0] data;

output open;

parameter Idle = 2'b00,

Detect_Three = 2'b01,

Detect_Two = 2'b10,

Detect_One = 2'b11;

reg[1:0] state;

reg[1:0] next_state;

always@(posedge clk or negedge reset)

if(!reset)

state = Idle;

else

state = next_state;

//-------------------next_state generate--------------

always(state or data)

case(state)

Idle:if(data==4'b0011)

next_state = Detect_Three;

else

next_state = Idle;

Detect_Three:if(data==4'b0010)

next_state = Detect_Two;

else

next_state = Idle;

Detect_Two:if(data==4'b0001)

next_state = Detect_One;

else

next_state = Idle;

Detect_One:if(data==4'b0011)

next_state = Detect_Three;

else

next_state = Idle;

default: next_state = Idle

endcase

//------------------output generate-------------

always@(state or reset)

if(!reset)

open = 1'b0;

else if(state==Detect_One)

open = 1'b1;

else

open = 1'b0;

endmodule

module number_locker_test;

reg clk,reset;

reg[3:0] data;

wire open;

always #5 clk = ~clk;

initial

begin

clk=0;

data=0;

reset=1;

#25 reset=0;

#200 reset=1;

#50;

serial_data_input(4'h0,4'h1,4'h3,4'h2,4'h1,4'h3,4'h3,4'h1,);

#100 $stop;

end

task serial_data_input;

input[4:0] d0,d1,d2,d3,d4,d5,d6,d7;

begin

data=d0;

#10;

data=d1;

#10;

data=d2;

#10;

data=d3;

#10;

data=d4;

#10;

data=d5;

#10;

data=d6;

#10;

data=d7;

#10;

endtask

number_locker U_number_locker(clk,reset,data,open); endmodule

请问在Verilog中模块源代码和测试模块源代码关系

首先,模块源代码描述了一个电路,这个电路要工作,肯定需要一个外部环境(比如clk信号的输入之类的),然后,这个电路的输出我们也希望能查看。

在实际烧写进FPGA之前,我们希望用一个软件来模拟这个电路工作的情况,也就是所说的仿真。

然后,测试代码(testbench)是用来模拟源代码所实现的电路的外部环境的,也可以通过软件来查看这个电路的输出信号的波形。

所以,不写测试代码,只要你能保障源代码正确无误,是可以不用仿真的(但说实话,谁能保证呢,除非电路太简单了)。

另外,由于模块的源代码是要生成具体器件的,所以必须是可综合的。而测试代码只是模拟外部环境,所以不需要是可综合的。

用verilog设计一个4*4矩阵键盘,来对模拟开关进行控制从而实现对输入电压不同倍数的放大

从程控放大电路的实际应用来讲,楼主所作的方案没有什么必要。当然,就题目来讲,一个经典的4*4矩阵键盘可以一键输入0~F的信息,还是很有价值的。原来也没有作过这方面的东西,尝试着在网络上找了别人的文档,感觉如下链接交待的最好,它不仅有4*4矩阵键盘外围电路的示意图,也有关于代码的流程图说明(当然对于verilog设计--即作为硬件来讲,把它表述成为状态图会更好),还有对于所设计模块接口信号的简单说明。可以一起学习一下。

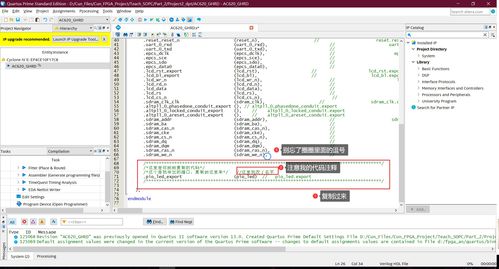

我做verilog HDL的练习题,简单时序逻辑电路的设计,在quartus中做的代码在modelsim仿真时出现了错误!

首先,在测试模块下,你的输入时钟为clk_in,而不是clk,所以应该把 clk = ~clk;替换为clk_in=~clk_in;在initial下把clk=0改成clk_in=0;另外,在modelsim下创建testbench的时候,由source——show language templates可以得到测试模块的模板,只需对输入进行定义和初始化,以下是我做修改后在modelsim6.2下的测试模块的程序:

`timescale 1ns/100ps

`define clk_cycle 50

module half_clk_tb ;

reg clk_in ;

wire clk_out ;

reg reset ;

always #`clk_cycle clk_in = ~clk_in;

initial

begin

clk_in = 0;

reset = 1;

#100 reset = 0;

#100 reset = 1;

#10000 $stop;

end

half_clk

half_clk (

.clk_in (clk_in ) ,

.clk_out (clk_out ) ,

.reset (reset ) );

endmodule

以下插图是我仿真后的结果:

放大器verilog源代码的介绍就聊到这里吧,感谢你花时间阅读本站内容,更多关于比较器verilog代码、放大器verilog源代码的信息别忘了在本站进行查找喔。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

相关推荐

- 05-09网页代码,网页代码快捷键

- 05-07pb超级报表源代码(pb报表工具)[20240507更新]

- 05-07简历源代码可以上传照片的简单介绍[20240507更新]

- 05-07广告切换源代码免费下载(广告切换源代码免费下载安装)[20240507更新]

- 05-06单页网站的代码(完整的网页代码)[20240506更新]

- 05-06阁楼网源代码(阁楼是什么网站)[20240506更新]

- 05-06个人主页图片代码(个人主页图片代码怎么弄)[20240506更新]

- 05-06提取微信名片代码(微信名片信息提取)[20240506更新]

- 05-06php后台权限管理代码(php管理员权限)[20240506更新]

- 05-06付费观看代码php(付费观看代码)[20240506更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接