verilog经典代码(verilog 版本)

admin 发布:2022-12-19 18:48 171

今天给各位分享verilog经典代码的知识,其中也会对verilog 版本进行解释,如果能碰巧解决你现在面临的问题,别忘了关注本站,现在开始吧!

本文目录一览:

- 1、求verilog的一段代码

- 2、关于Verilog基础代码问题

- 3、哪位高手能帮忙解读一下下面这段verilog代码?

- 4、用verilog代码编写下面的程序

- 5、verilog代码

- 6、如何写出高质量的verilog代码

求verilog的一段代码

你不给DA,AD的型号怎么写

DA,AD的实验我都做过,基于SPI接口的.

给你个我调试通过的DA控制的程序吧,稍微简单点,型号LTC2624,串行输出,时钟5MHz,采用32位协议

module dac1(databus,clk,clr,serial_out,start,dac_cs,dac_clr,spi_ss_b,amp_cs,ad_conv,sf_ce0,init_b);

input clk,clr,start;//clk是DA控制器的时钟,也是DA的时钟.没有在输出里面声明,需要在外部模块加入.

input [11:0] databus;//数据总线

output serial_out,dac_cs,dac_clr,spi_ss_b,amp_cs,ad_conv,sf_ce0,init_b;//serial_out是输出给DA的串行数据,dac_cs是da的转换信号,一帧数据接受完毕后拉高,dac_clr是清空dac内部的寄存器,其他是SPI总线复用信号,可以忽略

reg [2:0] state,next_state;

parameter idle=3'b001;

parameter load2=3'b010;

parameter send=3'b100;

reg spi_ss_b;

reg amp_cs;

reg ad_conv;

reg sf_ce0;

reg init_b;

reg dac_cs;

reg dac_clr;

reg shift;

reg clear;

reg load;

reg [5:0] bit_counter;

reg [31:0] data_shfreg;

assign serial_out=data_shfreg[31];

always@(state or bit_counter or start)

begin

spi_ss_b=1;

amp_cs=1;

ad_conv=0;

sf_ce0=1;

init_b=1;

load=0;

shift=0;

clear=0;

next_state=state;

case(state)

idle: if(start==1)

begin

load=1;

next_state=load2;

end

load2: begin

load=1;

shift=1;

next_state=send;

end

send: if(bit_counter!=6'b100000)

shift=1;

else

begin

clear=1;

load=1;

next_state=load2;

end

default next_state=idle;

endcase

end

always @(posedge clk)

if(clr)

dac_clr=0;

else

dac_clr=1;

always @(posedge clk or posedge clr)

if(clr)state=idle;else state =next_state;

always @(posedge clk or posedge clr)

begin

if(clr)begin

data_shfreg=0;

bit_counter=0;

end

else

begin

if(load)

data_shfreg={8'b11111111,4'b0011,4'b1111,databus[11:0],4'b1111};//32位协议格式

if(clear)bit_counter=0;

else if(shift)bit_counter=bit_counter+1;

if(shift)

data_shfreg={data_shfreg[30:0],1'b1};

if(shift)

dac_cs=0;

else

dac_cs=1;

end

end

endmodule

关于Verilog基础代码问题

这个代码功能应该是完成数据高低位的互换。verilog的写法类似于C/C++,所以if(a)其实是if(a==1'b1)的缩写,即a为高电平时,执行寄存器高低位互换语句。可以将a信号理解为一个使能控制信号。

哪位高手能帮忙解读一下下面这段verilog代码?

这个是一个vitebi解码器的tbu模块。tbu里面实例化了一个traceunit作为testbench。这个traceunit的定义在第二个模块里面,主要就是一个状态转换的逻辑。

用verilog代码编写下面的程序

这就是把ABC三个电台的启动信号变为输入,XY的启动信号为输出,列出真值表就行了吧。

真值表为:

a

b

c

x

y

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

verilog代码

module test(

input [1:0] ina,

input [1:0] inb,

input in_sel,

input clk,

input clear,

output reg out_a,

output reg out_b

);

wire eq0,eq1,eq2,eq3;

wire [1:0] result;

wire d1;

wire d2;

assign result = (in_sel)?inb:ina;

assign {eq3,eq2,eq1,eq0} = (result == 2'b0) ?{3'b0,1'b1}

(result == 2'b1) ?{2'b0,1'b1,1'b0} :

(result == 2'b2) ?{1'b0,1'b1,2'b0}:

{1'b1,3'b0};

assign d1 = ~(eq0 | eq1);

assign d2 = ~(eq2|eq3);

always @(posedge clk or posedge clear)

begin

if(clear == 1'b1)

begin

out_1=1'b0;

out_2=1'b0;

end

else

begin

out_1= d1;

out_2 = d2;

end

end

endmodule

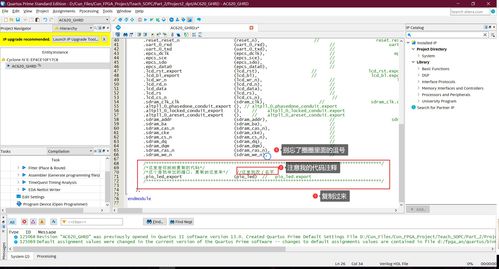

如何写出高质量的verilog代码

verilog的代码其实是电路,所以你写的时候需要对你生成的电路有一定的概念。其次多看看综合的结果,然后明白具体实现的结果有什么不同。再有就是多看看优秀的verilog设计,sundesignburst的那几个设计文件是经典的设计。

verilog经典代码的介绍就聊到这里吧,感谢你花时间阅读本站内容,更多关于verilog 版本、verilog经典代码的信息别忘了在本站进行查找喔。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

相关推荐

- 05-09网页代码,网页代码快捷键

- 05-06单页网站的代码(完整的网页代码)[20240506更新]

- 05-06个人主页图片代码(个人主页图片代码怎么弄)[20240506更新]

- 05-06提取微信名片代码(微信名片信息提取)[20240506更新]

- 05-06php后台权限管理代码(php管理员权限)[20240506更新]

- 05-06付费观看代码php(付费观看代码)[20240506更新]

- 05-06在线html执行代码(html怎么运行)[20240506更新]

- 05-06源代码管理资源管理器(资源管理器运行代码)[20240506更新]

- 05-06代码源软件库(程序代码库)[20240506更新]

- 05-06点击弹出密码代码(点击弹出密码代码错误)[20240506更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接