veriloghdl代码(verilog hdl代码)

admin 发布:2022-12-19 15:38 136

今天给各位分享veriloghdl代码的知识,其中也会对verilog hdl代码进行解释,如果能碰巧解决你现在面临的问题,别忘了关注本站,现在开始吧!

本文目录一览:

- 1、采用 Verilog HDL 语言设计带异步清0、异步置1 端的边沿触发型T 触发器。求代码

- 2、用Verilog HDL语言设计一个模值可变的计数器?怎样做?

- 3、用verilog hdl语言编写一个8—3译码器程序

- 4、基于fpga的动态目标跟踪的VerilogHDL代码

- 5、Verilog HDL 简单六人抢答器代码?

采用 Verilog HDL 语言设计带异步清0、异步置1 端的边沿触发型T 触发器。求代码

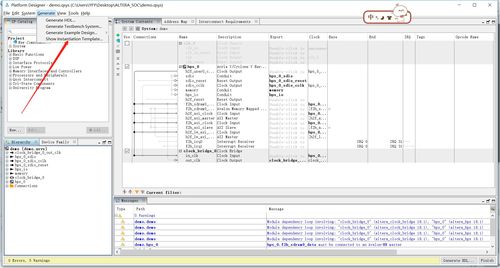

首先,你可以利用QUARTUS里面,tools菜单里的mega

wizard功能来产生系统自带的各类触发器,应该是各种类型的触发器都有。下面简单编写verilog代码,假设是1位T触发器。

module

T(rst1,rst0,clk,in,out)

input

rst,rst0,clk,in;

output

out;

reg

out;

always

@(posedge

clk

or

negedge

rst1

or

negedge

rst0)

begin

if(rst1)

out=1;

else

if(rst0)

out=0;

else

begin

if(in)

out=in;

else

out=out;

end

end

endmodule

你调试一下,欢迎追问~

用Verilog HDL语言设计一个模值可变的计数器?怎样做?

其实很简单的,这个和可以设置初始值的计数器实现方法是一样的。如果你能看懂下面这段代码,相信你肯定能写出一个模值可变的计数器了。

module counter7(clk,rst,load,data,cout);

input clk,rst,load;

input [2:0] data;

output reg [2:0] cout;

always@(posedge clk)

begin

if(!rst)

cout=3’d0;

else if(load)

cout=data;

else if(cout=3’d6)

cout=3’d0;

else

cout=cout+3’d1;

end

endmodule

这段代码是设计一个可预置初值的7进制循环计数器。按照你的需要,稍微改一下就可以了,这下你应该会了吧?

用verilog hdl语言编写一个8—3译码器程序

首先要纠正一下,相对多的输入转化成为相对少的输出,一般叫编码器;相对少的输入转化成为相对多的输出,一般叫译码器。所以,确切地说你要做的应该是8-3编码器(还是3-8译码器)。

//8-3编码器verilog代码

module enc_83(datain, dataout, en);

input [7:0] datain;

input en;

output [2:0] dataout;

reg [2:0] dataout;

always @*

if (~en)

dataout = 3'b0;

else case(datain)

8'b0000_0001: dataout = 3'b000;

8'b0000_0010: dataout = 3'b001;

8'b0000_0100: dataout = 3'b010;

8'b0000_1000: dataout = 3'b011;

8'b0001_0000: dataout = 3'b100;

8'b0010_0000: dataout = 3'b101;

8'b0100_0000: dataout = 3'b110;

8'b1000_0000: dataout = 3'b111;

default: dataout = 3'b000;

endcase

endmodule

//关于上述代码的说明

1) 上述实现的是8-3普通编码器,即同一时刻输入保证只有一位有效;

2) 上述代码没有输出编码有效的标识位,如果需要的话可自行添加。

基于fpga的动态目标跟踪的VerilogHDL代码

#include iostream

using namespace std;

class Coordinate

{

// 友元函数

friend void display(Coordinate coor);

public:

Coordinate(int x, int y)

{

m_iX = x;

m_iY = y;

}

public:

int m_iX;

int m_iY;

};

void display(Coordinate coor)

{

cout "m_iX:" coor.m_iX endl;

cout "m_iY:" coor.m_iY endl;

}

int main(void)

{

Coordinate coor(1,2);

display(coor);

return 0;

}

Verilog HDL 简单六人抢答器代码?

这样设计:

定义6个人分别为a,b,c,d,e,f (即:输入) 对应的6展灯分别为 a0,b0,c0,d0,e0,f0(即:输出)

抢答器复位信号rst(输入,每次抢答结束会复位抢答器进行下轮抢答)

逻辑时钟输入clk

然后开始写代码:

moudle(a,b,c,d,e,f,a0,b0,c0,d0,e0,f0);

input a,b,c,d,e,f,rst,clk;

output a0,b0,c0,d0,e0,f0;

reg lock; //设计的关键,只有第一个抢答的人有效

always(posedge clk or nengdge rst)

begin

if(~rst)

begin

a0 = 1'b0;

b0 = 1'b0;

c0 = 1'b0;

d0 = 1'b0;

e0 = 1'b0;

f0 = 1'b0;

lock = 1'b0;

end

else if (~lock)

begin

if(a)

begin

a0 = 1'b1;

lock = 1'b1;

end

if(b)

begin

b0 = 1'b1;

lock = 1'b1;

end

if(c)

begin

c0 = 1'b1;

lock = 1'b1;

end

if(d)

begin

d0 = 1'b1;

lock = 1'b1;

end

if(e)

begin

e0 = 1'b1;

lock = 1'b1;

end

if(f)

begin

f0 = 1'b1;

lock = 1'b1;

end

end

end

endmoudle

veriloghdl代码的介绍就聊到这里吧,感谢你花时间阅读本站内容,更多关于verilog hdl代码、veriloghdl代码的信息别忘了在本站进行查找喔。

版权说明:如非注明,本站文章均为 AH站长 原创,转载请注明出处和附带本文链接;

- 上一篇:心情说说asp源代码的简单介绍

- 下一篇:joomla建站代码下载的简单介绍

相关推荐

- 05-09网页代码,网页代码快捷键

- 05-06单页网站的代码(完整的网页代码)[20240506更新]

- 05-06个人主页图片代码(个人主页图片代码怎么弄)[20240506更新]

- 05-06提取微信名片代码(微信名片信息提取)[20240506更新]

- 05-06php后台权限管理代码(php管理员权限)[20240506更新]

- 05-06付费观看代码php(付费观看代码)[20240506更新]

- 05-06在线html执行代码(html怎么运行)[20240506更新]

- 05-06源代码管理资源管理器(资源管理器运行代码)[20240506更新]

- 05-06代码源软件库(程序代码库)[20240506更新]

- 05-06点击弹出密码代码(点击弹出密码代码错误)[20240506更新]

取消回复欢迎 你 发表评论:

- 标签列表

- 最近发表

- 友情链接